利用一種創新的軟件擴展增加設計驗證功能,可以在

PCB設計的原理圖擷取階段實現可測試性設計(DFT)途徑。

「確保設計正確」(right by design)這個概念意味著業經討論的設計總會如預期般地順利作業,因此,一旦設計「正確」,就不需要測試了。原則上,雖然確實如此,測試并不是發現設計缺陷的主要手段,它只是產品開發中的一個環節。

雖然在任何時候都可能出現新的「缺陷」,但在設計階段之后出現的故障完全有可能是由制造過程引起的,特別是對于成熟的產品來說。例如,發生在波焊(wave soldering)過程中的潛在制造缺陷就可列出一長串的清單,包括:不完整的焊點、干裂或球形焊點、焊盤或阻焊劑隆起、焊盤污染、錫球;當然還有開路和焊接短路。

上述任何缺陷都可能讓電路板(PCB)停擺,有些問題則可能等到交貨很長一段時間后才被發現。采用「可制造性設計」(DFM)方法有助于使發生這類缺陷的可能性降至最低,這些措施一般最佳應用在PCB布局階段。透過現代設計工具在此階段施加一些設計規則,有助于實現DFM的自動化。

不管電路板的布局設計得多好,制造過程中的缺陷都是不可避免的,因此必須在產品出貨前透過測試途徑發現。采用可測試性設計(DFT)途徑可以確保檢測和定位出制造缺陷,即使故障發生在表面黏著元件之下。相較于嚴格的設計「規則」——如走線間的最小間距或在指定層上的布線,DFT途徑需要更早更廣泛的采用,并在原理圖擷取階段進行建置。

DFT確保設計正確

可測性設計也許比可制造性設計的主觀性更強。由于受到成本、空間或復雜度的限制,對于某一項設計看似正確的方法,對另一個設計來說可能是不正確的。然而,IC制造商們幾乎一致同意的是,在復雜的整合元件中包含邊界掃描等DFT技術如今已經成為常態。

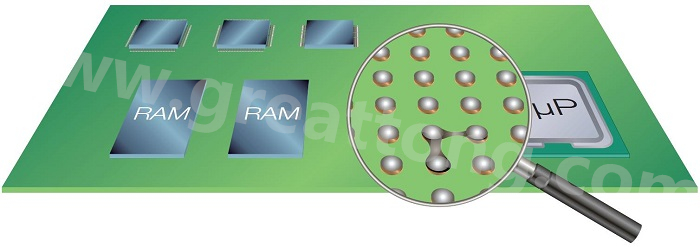

雖然JTAG經常用于除錯執行于微處理器上的軟件,但邊界掃描具有更寬的應用范圍。邊界掃描的開發主要用于發現「隱藏」在先進的表面黏著元件(通常是球閘陣列或BGA元件)下方的制造缺陷。

邊界掃描提供的測試存取層級明顯高于其它許多測試形式,也更具成本效益,因為它「內建」于元件之中,因而不至于增加這些元件的成本。大多數的FPGA/CPLD和處理器(包括微控制器)以及一些固定功能的元件(如乙太網路收發器、介面控制器和PCI Express PHY)現在都建置了邊界掃描功能。

存取一款制造產品中的邊界掃描功能,必須采用合適的專業硬體和軟件,并確保設計可提供這種存取是免費的;它只要求在開發的原理圖擷取階段采用DFT途徑。試圖在PCB布局設計期間或其后建置或校正邊界掃描鏈是沒有用的;確保在原理圖擷取期間的設計正確、更加簡單,因而也更具成本效益。

實現正確的設計掃描鏈

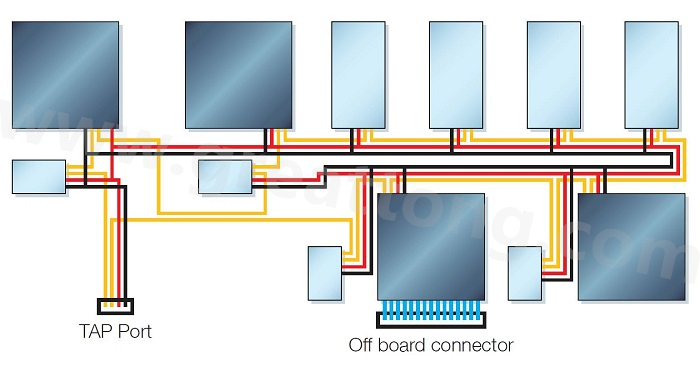

邊界掃描要用專門的匯流排實現,這種匯流排由4個或5個訊號組成。這些訊號統稱為測試接取埠(TAP),必須正確地連接到菊鍊配置(即掃描鏈)中所有具有JTAG功能的IC。TAP先從連接器布線到掃描鏈中的第一個IC,然后到第二個,以此類推,一直到掃描鏈中的最后一個IC后再回到連接器。

圖1:邊界掃描鏈依序連接PCB上具有JTAG功能的元件,從而進行測試存取以執行連接與功能測試

掃描鏈的順序特性意味著邊界掃描測試圖案必須通過每個元件,然后返回連接器。因此,掃描鏈中必須毫無中斷或脆弱的連接。這將帶來許多DFT的考慮因素,例如確保掃描鏈連接到設計中每個具有JTAG介面的IC、掃描鏈中TAP訊號必須正確連接到這些IC的正確接腳,以及TAP訊號使用了建議的的終端連接。

除了定義TAP的電氣特性,IEEE 1149.1(邊界掃描)標淮還定義了掃描鏈的協定。這有助于辨識元件、用于TAP的接腳以及元件支援的測試功能。這些資訊儲存在一個稱為邊界掃描描述語言檔(BSDL)的專用檔案中;相容JTAG的每個IC都必須有一個與之相關的BSDL檔。儲存在這個檔案中的資訊可以讓專業的軟硬體供應商開發出在測試過程中用于存取和控制JTAG元件的產品。

DFT的自動化

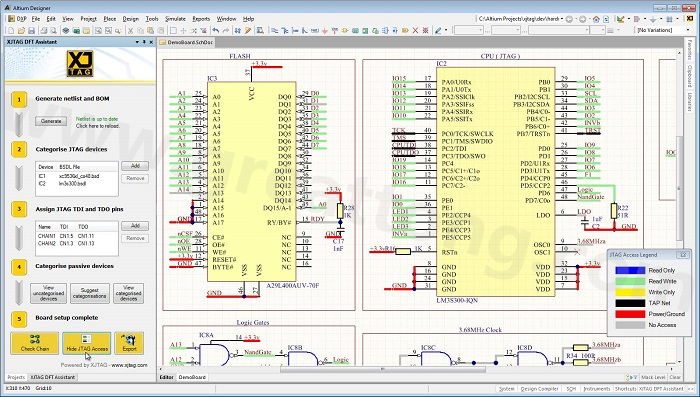

檢查掃描鏈中所有JTAG元件是否正確連接通常是一個人為的過程,因此就像其它任何人工設計過程一樣極易于發生人為錯誤。但最近已經能為邊界掃描鏈實現自動化的設計驗證了。藉由其邊界掃描測試的專業技能,XJTAG已經為Altium Designer開發出免費的軟件擴展,以輔助邊界掃描鏈的設計驗證,從而使得這個設計環境的DFT性能達到了全新的層次。

這個軟件擴展被稱為XJTAG DFT Assistant,它使用Altium Designer在原理圖擷取階段產生的網表,形成了掃描鏈如何在設計中進行連接的簡圖。再透過將BSDL檔案導入專案中進行補充,讓它理解掃描鏈應該如何布線。如此一來,擴展功能不僅可以檢查原理圖中的掃描鏈連接,還能顯示提供給邊界掃描軟硬體的測試存取層級。

圖2:邊界掃描可以找出「隱藏」在BGA下方的制造缺陷

這一軟件擴展透過兩個主要的功能達到目的:XJTAG Chain Checker和XJTAG Access Viewer。所收集的資料還可以匯出,用于XJTAG的邊界掃描測試開發環境XJDeveloper。因此,它可為JTAG元件和非JTAG元件支援邊界掃描測試功能的開發。如果在設計時考慮邊界掃描測試功能,就可以擴展測試存取到更多的電路。藉由XJTAG Access Viewer功能,設計人員可以監測、評估和儘量提高在原理擷取階段的測試存取能力,這是在導入這種免費的軟件擴展之前無法自動驗證的功能。

其關鍵在于這種軟件擴展還能夠在PCB設計進入布局階段之前,及早檢測出掃描鏈中的錯誤。藉由使其成為設計過程的一部份,XJTAG DFT Assistant有助于讓設計人員避免阻止掃描鏈作業中常見的故障,例如錯誤的TAP訊號布線或訊號端接不良。也許更重要的是,它能提示電路板設計人員哪些IC可以存取邊界掃描測試,從而標示出應該連接的所有IC,以及哪些IC或設計區域目前無法存取邊界掃描測試,但可以透過設計修改進行存取。

隨著設計的進展,這些功能可以反覆使用,從而確保盡可能地利用測試存取功能,以及使邊界掃描鏈得到正確的設計。開發人員手中掌握這些資訊不僅有助于其更加明白如何建置邊界掃描,也有利于在原理圖設計中實現整個DFT途徑的自動化。

圖3:XJTAG DFT Assistant的Access Viewer模式可以清楚地顯示可用的測試存取層級,讓電路板設計人員在展開PCB布局以前的原理圖擷取階段盡可能地提高測試存取能力

了解邊界掃描和BSDL檔案有助于像XJTAG等業者開發出從原型到量產的整個產品生命周期中都必須使用邊界掃描功能的軟硬體產品。利用這種專業知識為Altium Designer開發免費的擴展軟件,開發人員現在可以存取功能強大的設計驗證技術,大幅提高第一次就成功的開發能力。

深圳宏力捷推薦服務:PCB設計打樣 | PCB抄板打樣 | PCB打樣&批量生產 | PCBA代工代料