最近,多核心系統單晶片(SoC)元件的出現重新劃分了硅元件、電路板和子系統之間的界線。這種趨勢導致晶片-晶片和電路板-電路板的互連要求發生了重大變化。那么,現有標淮已淮備好應對這一變革了嗎?

1970年代,由于微處理器的問世,利用分離式處理器、記憶體控制器和I/O介面元件,在單一電路板上就可以建構簡單的運算系統。由板級匯流排來連接這些元件,而當需要更高性能時,便將多塊

電路板組裝在一起,利用系統級匯流排透過背板提供卡間通訊。

這些電路板和系統互連協議都是專用的。但隨后,專用協議逐漸讓位于標淮化協議,如以太網絡、PCI Express或RapidIO協議。

與此同時,積體電路技術遵循摩爾定律,其包含電晶體的數目和速度不斷增加。這些趨勢大幅推動了處理器性能的提升。

迄今已有數代硅元件充分利用了這一良性周期。不幸的是,單核心處理器的性能提高速度已開始趨于下滑。造成這種下滑的最重要因素一直是功耗。電晶體越小,開關速度越快。電晶體尺寸的縮小使泄漏增加,導致靜態功耗的增大。同時,隨著電晶體開關速度的加速,動態功耗也在增加。

這種不斷上升的功耗凸顯了目前硅制程技術存在的幾個現實問題。首先,單處理器的性能受功率和系統功耗限制。其次,電晶體預算持續增加,而可獲得的時脈速率卻不然。

隨著電晶體預算的持續增加,業界已迅速轉向具有多個處理器核心的元件。這些元件還整合記憶體控制器、應用加速器和I/O介面的元件,形成多核心SoC。多核心元件可望大幅提高系統性能。

SoC元件的問市模糊了單一元件及完整系統架構之間的界線。曾經在一個完整的運算系統中,需要用到一塊電路板,而現在只需要單顆元件,就能將多個系統囊括在內。

向SoC元件的轉換改變了SoC和其他元件及網路之間的互連要求。電路板和系統級互連最初基于匯流排共用,而且和以往的處理器一樣,采用一種類似的方式來滿足對更高互連性能的要求:增加時脈速率,加寬匯流排頻寬。然而,蹈處理器之覆轍,最后同樣因實體效應的影響,匯流排上的元件數目不得不減少,因而催生出了匯流排分割、分層化拓撲和最終的點對點開關網路。

嵌入式系統通常劃分為三種子系統:控制面、資料面和系統管理。當系統只包含一個運算系統時,系統級的通訊串流數目很有限。這是幸運的,因為按照定義,基于匯流排的互連只能容納一個通訊串流。

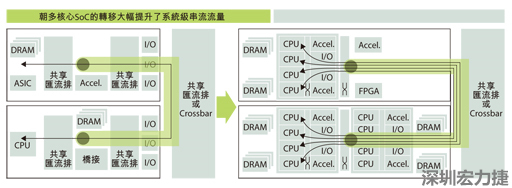

圖1:當系統只包含一個運算系統時,系統級的通訊串流數目很有限。在多核心SoC中,由于每個核心分別處理各自的通訊串流,有可能實現每晶片多個通訊串流。

QoS考量

過去,為了提高系統性能,每一個功能采用一個專用處理器。隨著多個并行通訊通訊串流的出現,這種做法導致服務品質(QoS)問題急劇增加。為了最佳化頻寬并防止各個通訊串流之間產生干擾,在許多情況下都使用了三種單獨的互連。在這些系統中,每一個處理器執行一個功能,并分別負責單一或最多很少幾個通訊串流。

然而,多核心SoC的問世使這種局面大為改觀。由于每個核心均可分別處理各自的通訊串流,故有可能在每顆晶片上實現多個通訊串流。

平行地執行現有程式碼,在單顆多核心SoC上實現控制、資料和管理面功能融合的這一近期目標,預計將作為多核心架構的權宜之計。這種方法可在一個四核心元件上產生至少三個以上的通訊串流。長遠來看,軟件將支援多核心,并回復到運用眾多核心執行離散資料或控制面板功能。在任一種情況下,不論何處采用多核心SoC都將出現多個通訊串流。隨著使用8、16甚至更多核心的下一代SoC問世,未來2-4年間,單顆元件所能支援的通訊串流數目將大幅增加。

目前的互連支援多個通訊串流嗎?答案是肯定的。透過在單一互連傳輸之前進行多工,可支援任何數目的通訊串流。但仍存在兩大挑戰:在目的節點如何對通訊串流進行多工分離,如何賦予每一個通訊串流獨特的服務參數,如保證頻寬和平均或最壞延遲?

要解決這些問題,協議需要具備好幾個功能。首先,這個協議必須能夠對各個通訊串流進行差異化。換言之,應該能夠檢查纜線上的資料封包,并決定其屬于哪一個通訊串流?其次,當資料封包透過互連傳輸時,必須能夠執行服務參數。這一點可透過控制仲裁和流量控制來實現。例如,穩健的SoC需要多個通訊流量控制機制,以限制互連上的一系列擁塞事件。這些機制可能包括鏈路到鏈路、端到端和進/出流量管理。

嵌入式系統中應用最廣泛的互連也許是以太網絡。以太網絡的可擴展性已在多年服務中得到了充分的證實。基本的Layer 2以太網絡訊框只支援資料報類型(datagram-style)的處理,而且沒有已定義的流量差異化頭欄位。但之后,從Layer 2的VLAN標簽到更廣泛的Layer 3 IP報頭中的‘5 Tuples(五元組)’,各種流量差異化方法被放在最高層。其中,‘五元組’方案可支援數百萬個通訊串流。

不幸的是,對以太網絡而言,QoS已證實是一個更大的挑戰。這是因為只有一個有限的鏈路級PAUSE-訊框協議可被采用,而缺乏廣獲采納的流量控制機制所致。在鏈路級之外,有少數可解決此一問題的解決方案正在獲得更多支持,其中包括在Layer 2采用VLAN優先順序標簽(802.1Q),或在Layer 2和Layer 3之間采用MPLS報頭。流量管理也是常用方法。通常,在封閉式嵌入式系統中僅能發現一部份的這類方案;針對以太網絡,目前尚未有特定的完整與一貫性的方法。

另一個問題的出現,是由于大部份在以太網絡上分層的方案往往采用軟件來實現。由于硬體支援較少,可獲得的QoS參數受通訊串流通過軟件堆迭時產生的延遲和延遲抖動所限制。

1999年定義的RapidIO互連規格代表了一種更先進的系統互連方案。在該規格的開發過程中,QoS曾是一個重要考慮事項,包含了好幾種流量控制機制,如重試(retry)和基于信用(credit-based)的鏈路級流量控制、端到端XON/XOFF和流量控制協議。

在嵌入式系統中廣獲采用的另一種互連技術是PCI Express (PCIe)。PCIe最初瞄淮PC和服務器市場,支援配置、事件消息發送和讀寫處理。這種技術在系統級的QoS支援很有限。在per-VC basis上有穩健的基于信用的鏈路級流量控制,足以實現點對點通訊。

在實際應用中,以太網絡可以實現穩健的流量差異化,但缺乏穩健的QoS特性。大多數PCIe實現方案都沒有流量差異化能力。PCIe的流量控制有限,似乎是針對未來多核心元件淮備最不足的元件。三者中RapidIO潛力最大,因為它支援三個具有優先順序之通訊串流上的數百萬個差異化流量,并支援穩健的QoS特性。

幸運的是,許多新興的多核心SoC都支援多個外部互連協議。如飛思卡爾的8核心QorIQ P4080就可針對此處提到的所有協議進行配置。

深圳宏力捷推薦服務:PCB設計打樣 | PCB抄板打樣 | PCB打樣&批量生產 | PCBA代工代料